Transistor sottili come un foglio di carta: la nuova tecnologia del MIT per i chip del futuro

I ricercatori hanno sviluppato una tecnica per far crescere strati di materiali 2D direttamente su chip di silicio, aumentando la densità e la potenza dei circuiti

![]()

Una nuova tecnologia di crescita e fabbricazione consente l’integrazione di materiali 2D direttamente su un circuito di silicio, il che potrebbe portare a chip più densi e potenti. Le applicazioni emergenti di intelligenza artificiale, come le chatbots, che generano un linguaggio umano naturale, richiedono chip per computer più potenti. Ma i chip a semiconduttore sono tradizionalmente realizzati con materiali sfusi, che sono strutture tridimensionali squadrate; quindi, impilare più strati di transistor per creare integrazioni più dense è molto difficile. Tuttavia, i transistor semiconduttori realizzati con materiali 2D ultrasottili, ciascuno con uno spessore di soli tre atomi, potrebbero essere impilati per creare chip più potenti. A questo scopo, i ricercatori del MIT hanno dimostrato una nuova tecnologia in grado di “far crescere” in modo efficace ed efficiente strati di materiali 2D a base di dicalcogenuro di metalli di transizione (TMD) direttamente sopra un chip di silicio lavorato per consentire integrazioni più corpose.

Il problema della temperatura

La crescita di materiali 2D direttamente su un wafer di silicio CMOS ha rappresentato una sfida importante perché il processo richiede solitamente temperature di circa 600 gradi Celsius, mentre i transistor e i circuiti di silicio potrebbero rompersi se riscaldati oltre i 400 gradi. Un wafer, in microelettronica, è una sottile fetta di materiale semiconduttore, come ad esempio un cristallo di silicio, sulla quale vengono realizzati dei chip o die con circuiti integrati attraverso drogaggi (con diffusione o impiantazione ionica), la deposizione di sottili strati di vari materiali, conduttori, semiconduttori o isolanti, e la loro incisione fotolitografica. Ora, il team interdisciplinare di ricercatori del MIT ha sviluppato un processo di crescita a bassa temperatura che non danneggia il chip. Questa tecnologia consente di integrare direttamente i transistor a semiconduttore 2D nei circuiti standard di silicio. In passato, i ricercatori hanno coltivato materiali 2D altrove e poi li hanno trasferiti su un chip o un wafer. Questo spesso causa imperfezioni che ostacolano le prestazioni dei dispositivi e dei circuiti finali. Inoltre, trasferire il materiale senza problemi diventa estremamente difficile su scala wafer. Al contrario, questo nuovo processo produce uno strato liscio e altamente uniforme su un intero wafer da 8 pollici.

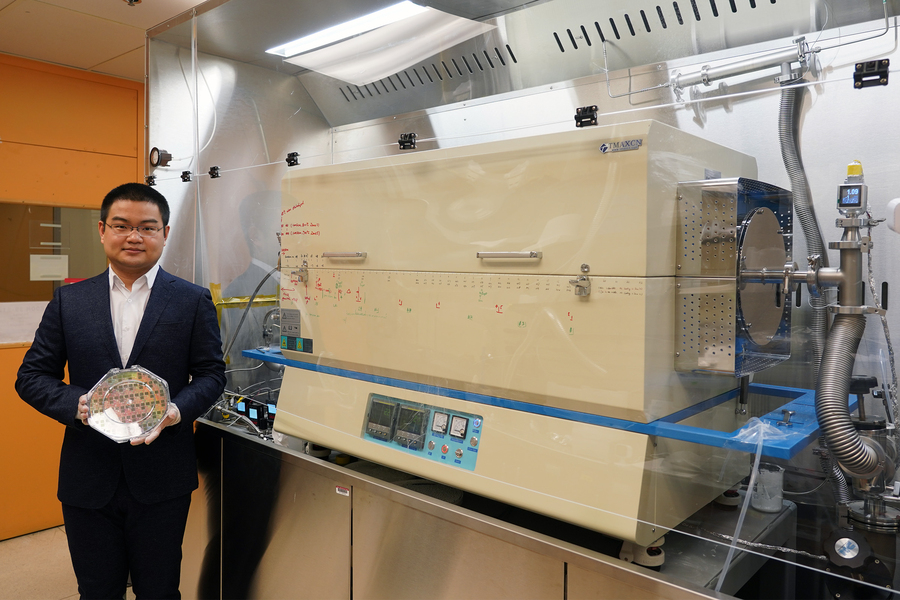

La nuova tecnologia è anche in grado di ridurre significativamente il tempo necessario per la crescita di questi materiali. Mentre gli approcci precedenti richiedevano più di un giorno per far crescere un singolo strato di materiali 2D, il nuovo approccio può far crescere uno strato uniforme di materiale TMD in meno di un’ora su interi wafer da 8 pollici. Grazie alla sua rapidità e all’elevata uniformità, la nuova tecnologia ha permesso ai ricercatori di integrare con successo uno strato di materiale 2D su superfici molto più ampie di quanto dimostrato in precedenza. Questo rende il loro metodo più adatto all’uso in applicazioni commerciali, dove i wafer da 8 pollici o poco più sono fondamentali. “L’uso di materiali 2D è un modo potente per aumentare la densità di un circuito integrato. Quello che stiamo facendo è come costruire un edificio a più piani. Se si dispone di un solo piano, che è il caso convenzionale, non potrà contenere molte persone. Ma con più piani, l’edificio conterrà un numero maggiore di persone che potranno realizzare cose nuove e sorprendenti. Grazie all’integrazione eterogenea su cui stiamo lavorando, abbiamo il silicio come primo piano e poi possiamo avere molti piani di materiali 2D direttamente integrati in cima“, ha dichiarato Jiadi Zhu, ingegnere elettronico ed informatico e coautore di un articolo su questa nuova tecnica. Il documento è pubblicato su Nature Nanotechnology.